近日,电子信息与电气工程学院微纳电子学系周健军教授课题组在IEEE Journal of Solid-State Circuits(JSSC)上发表题为“A 60MS/s 5MHz-BW Noise-Shaping SAR ADC with Integrated Input Buffer Achieving 84.2dB-SNDR and 97.3dB-SFDR Using Dynamic Level-Shifting and ISI-Error Correction”的模数转换器(ADC)芯片研究成果。

研究内容

该研究重点解决了ADC在系统应用中面临的集成输入缓冲器时的设计挑战,揭示了ADC符号间串扰的产生机理以及对ADC精度的影响,文章提出动态电平移位技术与采样误差校正技术,从而实现了片上集成缓冲器的高性能ADC的线性度提升。

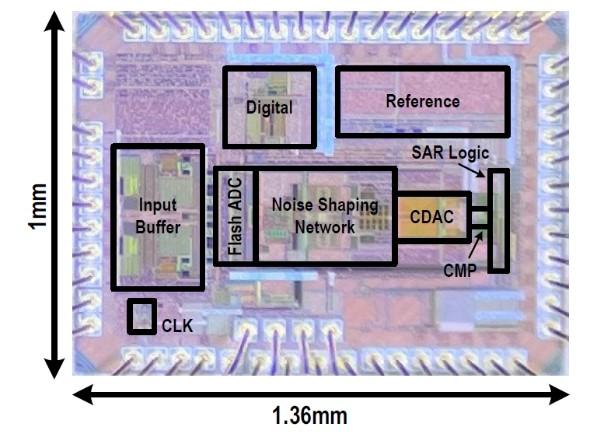

ADC芯片采用CMOS工艺流片验证,在采样率为60MS/s带宽为5MHz时,实现了84.2dB的SNDR和97.3dB的SFDR,达到了截止论文投稿时文献报道的集成了输入缓冲器的逐次逼近型ADC的最好优值指标(FoMw为60.6 fJ/conv.-step,FoMs为172.1dB)。此外,该芯片在设计时采用了多项数字辅助校准技术,并考虑了ESD保护等芯片可靠性问题。

集成输入缓冲器的逐次逼近型ADC芯片照片

关于JSSC

IEEE固态电路期刊(JSSC)是国际集成电路领域最高级别期刊之一,旨在发布集成电路设计领域的最新技术进展和纪录性成果,代表着业内当前最高技术水平。

作者信息

过悦康博士生是论文第一作者,金晶研究员为论文通讯作者。该项研究的参与人员全部来自上海交通大学微纳电子学系模拟射频集成电路设计中心实验室。该项研究受到国家自然科学基金项目资助。

论文链接:https://ieeexplore.ieee.org/document/9810848

以上内容由大学时代综合整理自互联网,实际情况请以官方资料为准。