8月8日,湖南大学段曦东教授课题组在国际顶级期刊《Nature Electronics》在线发表题为“Bilayer tungsten diselenide transistors with on-state currents exceeding 1.5 milliamperes perMicrometre”的研究论文。

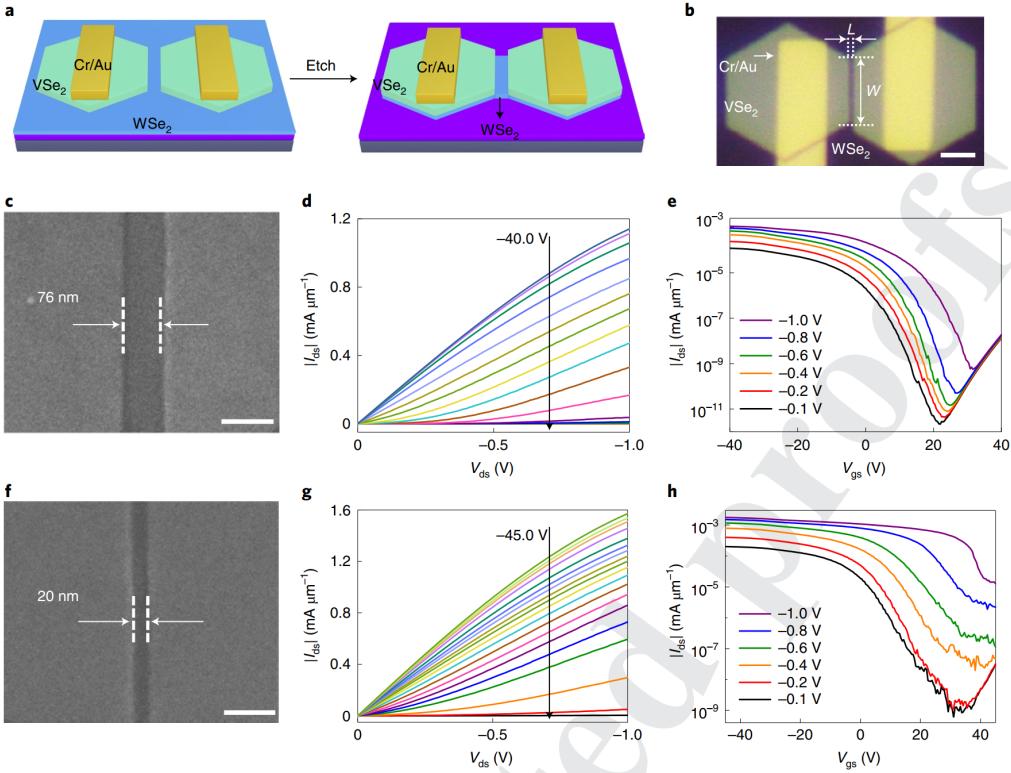

为了验证基于二维半导体晶体管性能确实能够取代或者超越传统硅基半导体,段曦东教授团队开发了原位生长金属二维半导体,构筑无损的范德华电接触技术,以此制备二维晶体管,有效避免传统光刻制造或金属集成工艺带来的表面污染、损伤和界面紊乱等问题,有利于表征二维半导体本征性能。团队进一步发展热应力可控产生晶界裂纹技术,控制相邻二维金属晶界间隙尺寸,自然定义了晶体管沟道。由此团队制备了沟道长度低于100nm的短沟道的、由二维金属形成范德华电接触的二维半导体晶体管原型管。团队在沟道长度为亚100纳米的二维半导体晶体管上普遍实现了大于1.50mA/μm的开态电流密度,特别是在20 nm的双层WSe2晶体管上实现了高达1.72mA/μm的开态电流密度的世界纪录。晶体管同时具有低于0.50kΩ·μm的开态电阻、高的开关比。工作首次证实二维晶体管已经达到取代目前先进制程硅基半导体器件水平。团队的工作以巧妙的实验设计,坚实的实验结果对领域内长期存在的“二维半导体晶体管究竟能否获得比拟或者优于传统硅基半导体晶体管的性能”的疑问做出了肯定的回答,必将吸引半导体、芯片领域的专家和产业界、投资界的注意,推动硅基半导体后的新一代二维半导体、芯片技术的发展。

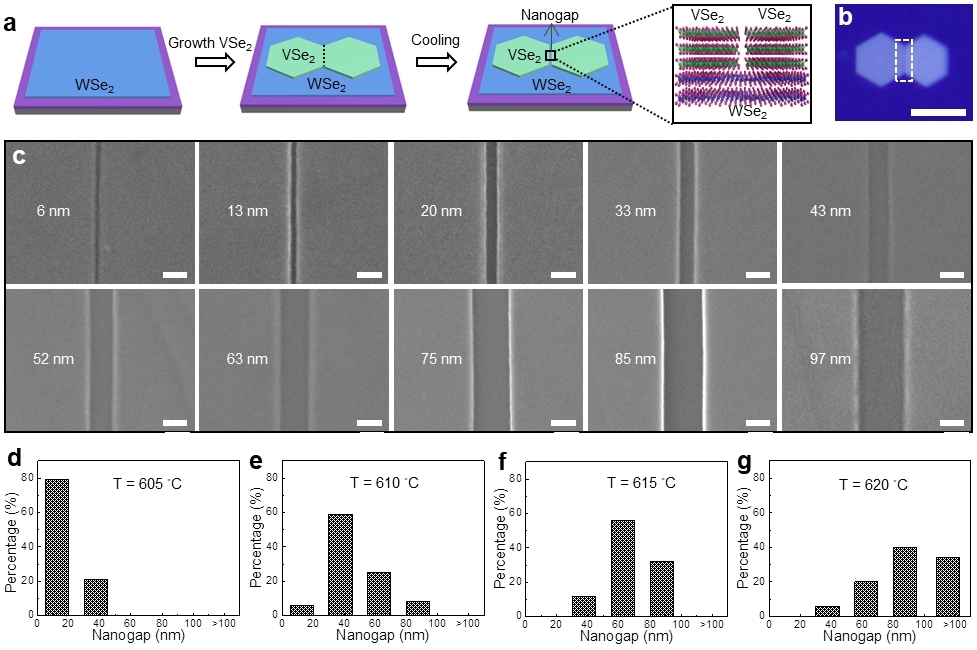

VSe2作为接触电极的双层WSe2短沟道生长调控。

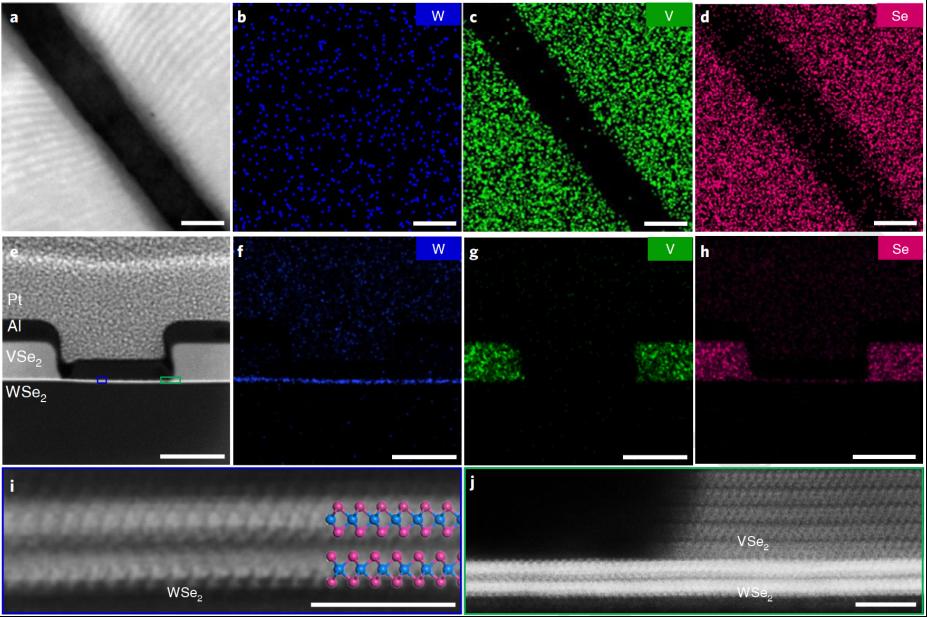

超短沟道双层WSe2晶体管的TEM表征。

二维半导体由于具有原子薄的厚度、表面可以原子级洁净、无悬挂键、在单个或几个原子层厚度下仍表现出优异的电学特性,可有效免疫短沟道效应,这些特性对于晶体管的持续微缩是必不可少的。这一想法已经在国际设备与系统路线图(IRDS)中得到表达。在大量的文献中使用许多不同的方法构造了基于二维半导体的晶体管,报道了二维半导体可以获得较高载流子迁移率或低接触电阻。但是载流子迁移率、接触电阻作为常用来评估二维半导体性能的参数都是经过复杂推导得到的,可能产生严重的误差,导致器件性能的评估模棱两可,有时甚至相互矛盾,从而引发了有关二维半导体究竟能达到怎样的极限性能、究竟能否取代硅基半导体的疑问。

为了回答此疑问并可靠地展示二维半导体晶体管的潜力,作者提出使用开态电流密度(Ion)或饱和电流密度提供一种更直接、更可靠的方法来评估二维半导体的实际潜力。Ion是晶体管的一个关键参数,它直接决定晶体管的速度和固有栅极延迟到。而且Ion是用仪表直接测量的,误差可控。此外,开态电阻(Ron)也是评估沟道材料的内在电势的重要性能参数。与迁移率或接触电阻相比,Ion或Ron是直接测量的参数,具有最简单的推导和较小的不准确性。

具体地,段曦东教授课题组在二维半导体WSe2沟道上直接通过化学气相沉积工艺(不进行直接光刻和金属化工艺以及带有机胶的转移工艺)制备了二维金属VSe2,形成双层WSe2晶体管的理想的范德华接触,极大地降低了接触电阻。在双层WSe2上范德华外延VSe2时,VSe2晶界处在冷却过程中由于VSe2和WSe2的热膨胀系数不同,晶界被拉开而自然形成亚100纳米间隙,自然定义了沟道长度。这样无需常规光刻或金属化工艺即可在原子级薄厚度的二维半导体材料WSe2上获得超短沟道(最短至6nm)晶体管。。扫描透射电子显微镜研究表明,所得的晶体管结构保留了原始的双层WSe2通道,并在双层WSe2与合成的VSe2触点之间具有原子清洁的界面,没有明显的污染或缺陷。对晶体管性能进行测量表明所得的低于100 nm的双层WSe2晶体管可以在1.0 V左右小的偏压下达到1.50 mA μm-1的超高Ion。特别是,在室温下,在沟道长度为20 nm,厚度为1.3 nm的双层WSe2晶体管中,获得了Ion为1.72 mA μm-1的单双层二维半导体晶体管开态电流密度的世界纪录。其中的Ron仅仅为0.50 kΩ·μm。该研究突破了二维晶体管的性能极限,首次证明了原子级厚度的二维晶体管在Ion方面与硅晶体管相比具有竞争优势,展示了二维半导体材料对于未来电子产品的巨大潜力。

超短沟道双层WSe2晶体管的电学性能测试。

超短沟道双层WSe2晶体管的性能突破。

以上内容由大学时代综合整理自互联网,实际情况请以官方资料为准。